Arrow Lake E-core Overclocking

We have a closer look at tuning the performance of the the Arrow Lake E-core, located on the Compute Tile.

Arrow Lake is Intel’s revolutionary new processor for mainstream desktop, featuring new P-cores and E-cores, disaggregated tile-based 3D Foveros packaging, an integrated NPU for AI acceleration, a next-generation uncore, DLVR power rails, and so much more.

In this blog post series, I have a closer look at Arrow Lake and explore its performance tuning and overclocking opportunities. I will cover the Compute (P-core, E-core, Graphics, NPU), Memory Subsystem (DDR, MC), and Data Fabric (Ring, NGU, D2D).

Arrow Lake E-core: Introduction

The Arrow Lake E-cores are located on the Compute Tile which is manufactured using the TSMC N3 process. It shares the tile with the P-cores, the Ring, and the caches.

An E-core cluster consists of four (4) E-cores. An Arrow Lake-S processor can have a maximum of four (4) E-core clusters yielding a total of sixteen (16) E-cores, like on the Core Ultra 9 285K. The E-cores feature the Skymont micro-architecture.

Arrow Lake E-core: Clocking

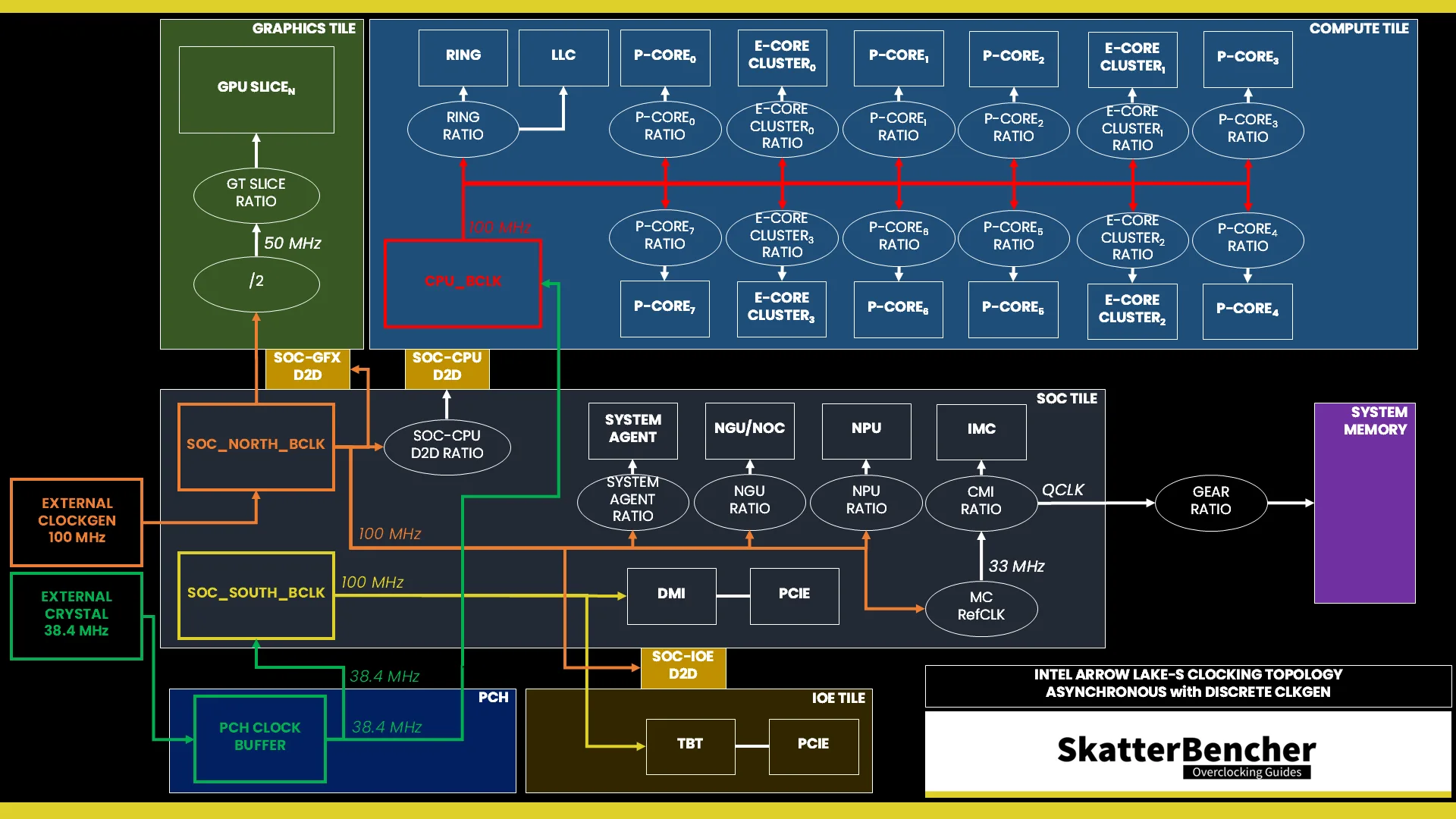

The clocking of the E-cores is similar to previous architectures: a reference clock is multiplied with a ratio to achieve the eventual operating frequency.

Reference Clock

The 100 MHz reference clock frequency is generated internally by the CPU PLL. This clock affects all IP blocks in the Compute Tile, including the P-cores, E-cores, and Ring. This PLL can be linked to the SoC PLL when you run in synchronous mode or work independently if you run in asynchronous mode.

You can configure the CPU BCLK frequency between 40 and 1000 MHz.

In the ASUS ROG BIOS, you can configure the CPU BCLK Frequency in the Ai Tweaker menu by first setting the Ai Overclock Tuner option to anything else than Auto.

You can switch between Asynchronous and Synchronous mode by adjusting the BCLK mode option.

E-core CPU Ratio

The reference clock is multiplied by the E-core cluster CPU ratio to achieve the final clock frequency. Each E-core cluster, consisting of four E-cores, can run at an independent clock frequency.

The effective E-core CPU Ratio is determined by three key inputs: the (adjusted) Turbo Ratio Limit, the (adjusted) Per Core Ratio Limit, and the Core Minimum Ratio. The final CPU ratio defined as the Max(MIN(aTRL,aPCRL), CMR).

Let’s have a look at each of these technologies.

Turbo Ratio Limit

Generally speaking, there are two ways to manually configure the CPU ratio on Intel platforms: sync all cores or use the Turbo Ratio Limit configuration.

- Sync All Cores sets a single fixed ratio applied to all cores. This is the historical method to get a static overclock.

- Turbo Ratio Limit configuration allows us to modify the default Intel frequency specification and configure a dynamic overclock.

On the Core Ultra 9 285K, the E-core Turbo Ratio Limit starts from 32X, which is the same as the advertised E-core base clock frequency. By default, the Core Ultra 9 285K E-cores can clock up to 4.6 GHz whether a single or all sixteen cores are active.

For the E-cores, we can configure eight different scenarios. Each scenario has a number of active E-cores and the target ratio. There’s a fixed logic ensuring the scenarios don’t overlap. So, the number of active cores of scenario n must be higher than the active cores for scenario n+1. Furthermore, the target ratio for scenario n must be higher than the target ratio for scenario n+1.

For example, we can create a scenario where 1 E-core boosts to 5 GHz, 5 E-cores boost to 4.8 GHz, 13 E-cores boost to 4.7 GHz and 16 E-cores boost to 4.6 GHz.

The E-core Turbo Ratio Limit configuration works independently from the P-core configuration. So, even if all P-cores are active, if one E-core is active it will set the frequency to 5 GHz.

The maximum Turbo Ratio Limit is 85X or 120X depending on whether Core Ratio Extension is enabled.

In the ASUS ROG BIOS, you can configure the E-Core Turbo Ratio Limits via the Ai Tweaker By E-Core Usage sub-menu.

Per Core Ratio Limit

Per Core Ratio Limit allows you to set a maximum CPU Ratio for every E-core cluster individually. It is an extension of the Intel Turbo Boost Max 3.0 technology introduced in 2016. It acts independently from the Turbo Ratio Limit, meaning that when you set a Per Core Ratio Limit, the E-core cluster ratio will be restricted even if the Turbo Ratio Limit allows for a higher boost frequency.

The Per Core Ratio Limit plays an important role in the Arrow Lake overclocking process. It’s not only the ratio used in the V/F point configuration but also the ratio referenced by many other ratio tuning technologies.

The maximum Per Core Ratio Limit is 85X or 120X depending on whether Core Ratio Extension is enabled.

In the ASUS ROG BIOS, you can configure the E-Core Per Core Ratio Limit via the Ai Tweaker Specific Efficient Core sub-menu.

Core Minimum Ratio

The Core Minimum Ratio is a brand-new feature for Arrow Lake. It allows you to set a CPU ratio floor for the P and E-cores. The floor value is still defined within the P-states, so it doesn’t prevent the cores from reducing their clock frequency in lower C-states when idling.

In other words, it’s not a replacement for disabling C-states in case you want to prevent core parking or cores from going to sleep.

In the ASUS ROG BIOS, you can configure the Minimum Turbo Ratio via the Ai Tweaker Tweaker’s Paradise sub-menu.

Granular Ratios

Granular Ratios are a brand-new overclocking feature for Arrow Lake. It adjusts the Per Core Ratio Limit by letting you set the CPU frequency in steps of 16.67 and 33.33 MHz.

The granular ratios can only be configured as a Per Core Ratio Limit, not as a Turbo Ratio limit. That’s because, technically, the granular ratios aren’t set directly but instead “down-binned” from the Per Core Ratio Limit. So, effectively, setting a granular ratio gives you an “adjusted Per Core Ratio Limit.”

For example, if you set a granular ratio of 50.16X. In that case, the Per Core Ratio Limit is set to 51X and then “down-binned” by 5 steps of 16.67 MHz (100 MHz divided by 6). That is important to keep in mind in case you’re also using other ratio configuration technologies.

In theory, you can set up to 255 down-bin steps from the Per Core Ratio Limit. That can lead to some errors in the software reading. Let’s say you set the Per Core Ratio Limit to 50X and then down-bin 200 steps of 16.67 MHz. Then, the operating frequency would be 1667 MHz instead of 5000 MHz.

Fortunately, you’ll find that most BIOSes give you a simple interface to set granular ratios.

In the ASUS ROG BIOS, you can configure the E-Core Granular Ratio via the Ai Tweaker Specific Efficient Core sub-menu.

OverClocking Thermal Velocity Boost

OverClocking Thermal Velocity Boost (OCTVB) allows us to reduce the CPU ratio at specified operating temperatures. While OCTVB is not new for Arrow Lake, it is available for the E-cores for the very first time.

To be more precise, OCTVB is available for the E-cores in “Per CCP Module” mode. That means it’s available as a configuration tool that down-bins from the Per Core Ratio Limit rather than from the Turbo Ratio Limit configuration. As a consequence, the configuration is done per E-core cluster.

Each E-core cluster has two available OCTVB points, each of which is defined by a target temperature and a number of down-bins. The temperature can be defined anywhere between 1 and 115 degrees Celsius. The down-bins can be defined between 0 and 31. Note that the down-bins are cumulative and thus the down-bins from point B stack on top of the down-bins from point A.

For example, let’s say we’ve set the E-core Cluster 0 Per Core Ratio Limit to 50X, set OCTVB Point A to -2X at 50C, and OCTVB Point B to -2X at 80C. In that case, the frequency will be 5 GHz below 50C, 4.8 GHz between 50C and 80C, and 4.6 GHz above 80C.

The OCTVB trigger point is the core-specific temperature. So, even if all other cores exceed the E-core cluster’s OCTVB temperature point, as long as the E-core cluster temperature does not exceed that temperature, it will not down-bin.

One last important thing to mention is that, for now at least, the temperature point is 5C off. By that, I mean that if you set the OCTVB point to 55C it actually kicks in at 60 degrees. That may be due to the TjMax increase from 100C on the previous generation Raptor Lake to 105C on Arrow Lake.

In the ASUS ROG BIOS, you can configure the Overclocking Thermal Velocity Boost Per CCP Module via the Ai Tweaker Thermal Velocity Boost sub-menu by first enabling Overclocking TVB and then setting OC TVB Configuration Limit to Per CCD Module.

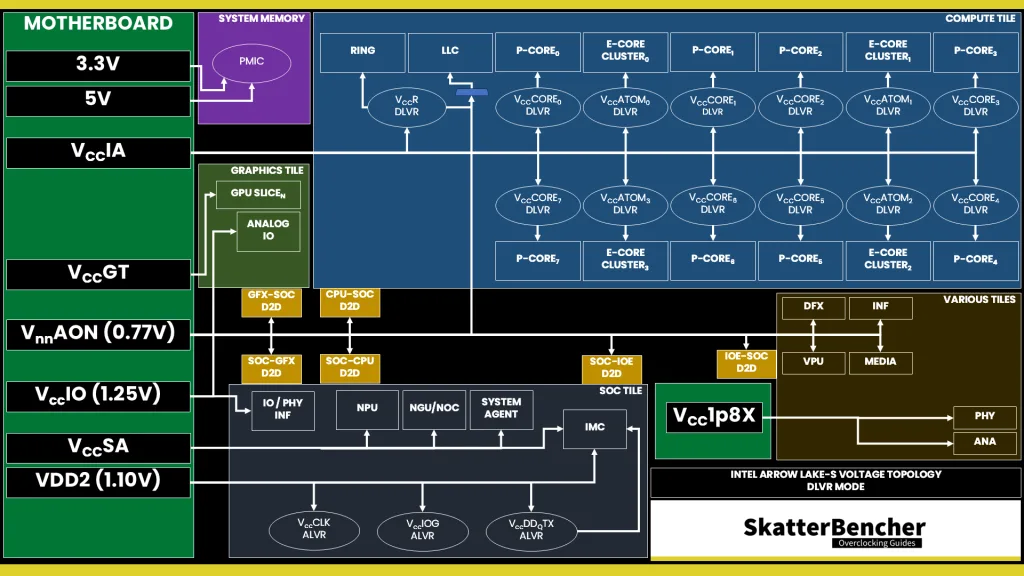

Arrow Lake E-core: Voltage

The voltage regulation for the E-cores is more complex than prior generations of Intel Core processors due to the introduction of the DLVRs. The DLVRs enable much lower voltage levels for the E-cores but still rely on a dynamic external motherboard voltage regulator as the input voltage source.

V/F Curve

Each Core Ultra 9 285K E-core cluster has its own V/F curve which is defined by up to seven (7) V/F points. The first six (6) V/F points are factory-fused, and the last point is mapped to the “OC Ratio.”

Here is the E-core V/F curve for my specific Core Ultra 9 285K. The voltage is about 650 mV at 800 MHz, then increases to 1.07V for VF Point 6 at 4.6 GHz. 4.6 GHz is the default maximum frequency for the E-cores.

In the ASUS ROG BIOS, you can find an approximation of the E-core’s V/F points (and thus V/F curve) in the Ai Tweaker Efficiency Core V/F Point Offset sub-menu.

Advanced Voltage Offset (V/F Points)

Advanced Voltage Offset, more commonly known as V/F Points, is available for each of the E-core clusters. There are seven (7) available VF Points, six of which are fixed to a specific ratio. The ratio is the same for all E-core clusters.

The final VF Point is mapped to the “OC Ratio” which is the E-core cluster Per Core Ratio Limit. If you use granular ratios, keep in mind those are down-binned from the next full ratio. In other words, the OC Ratio cannot be a granular ratio!

You can set a negative or positive voltage offset for each of these V/F points and for each of the E-core clusters. The final OC ratio’s base voltage will be the user-configured adaptive voltage.

In the ASUS ROG BIOS, you can configure the E-core V/F Points via the Ai Tweaker Efficient Core V/F Point Offset sub-menu.

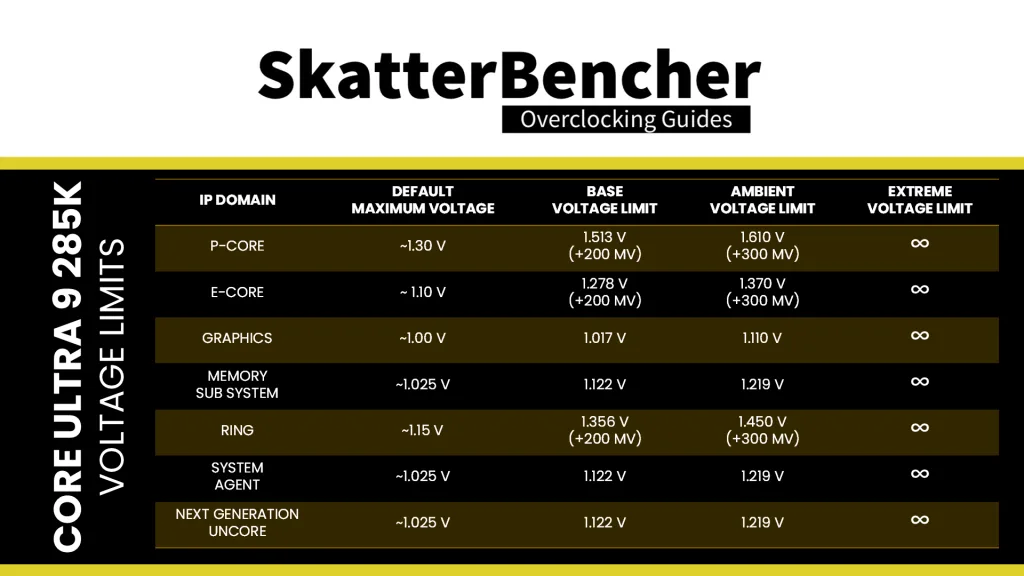

Voltage Limits

To safeguard the processor, Intel has imposed strict voltage limits for several IP blocks, including the E-core clusters. This limit effectively prevents E-cores from requesting a higher voltage from the PCU.

By default, the voltage limit for the E-cores is 1.278V, but this can be increased to 1.370V under ambient conditions. When the temperature is below 10 degrees Celsius, you can further increase the voltage limit or disable the limit altogether.

If you try setting the limit above the approved limit, the PCU will automatically adjust it to the highest allowed limit. If you disable voltage limits and the temperature is above 10 degrees Celsius, the CPU will operate in “safe mode” and limit the frequency to 400 MHz.

For DLVR-powered IP blocks like the E-core clusters, in theory, you can also change to PG mode to override the voltage limit and set any voltage you want. Of course, motherboard vendors can implement their own voltage limits for the voltage regulator.

In the ASUS ROG BIOS, you can configure the E-core Voltage Limit via the Ai Tweaker Max Voltage Limits sub-menu.

Thermal Velocity Boost Voltage Optimizations

Thermal Velocity Boost is an Intel technology that exploits the fact that CPUs need less voltage to run a specific frequency when the operating temperature is lower. When this technology is enabled, the CPU automatically adjusts the operating voltage according to the operating temperature. If you want manual control over the operating voltage to ensure stability, it’s prudent to disable this function.

When the voltage optimizations are enabled, we can use HWiNFO to track the CPU VID request as the CPU heats up. I’ve collected data for the Core Ultra 9 285K to illustrate this behavior. As you can see from the data, with the E-cores at 4.6 GHz, the operating voltage is 1.048V when the temperature is below 50 degrees Celsius. However, it increases to 1.068V when the temperature approaches 100 degrees Celsius.

A regression analysis tells us that the operating voltage changes 0.4 mV for every change in degree Celsius.

In the ASUS ROG BIOS, you can enable or disable the Thermal Velocity Boost Voltage Optimizations via the Ai Tweaker Thermal Velocity Boost sub-menu.

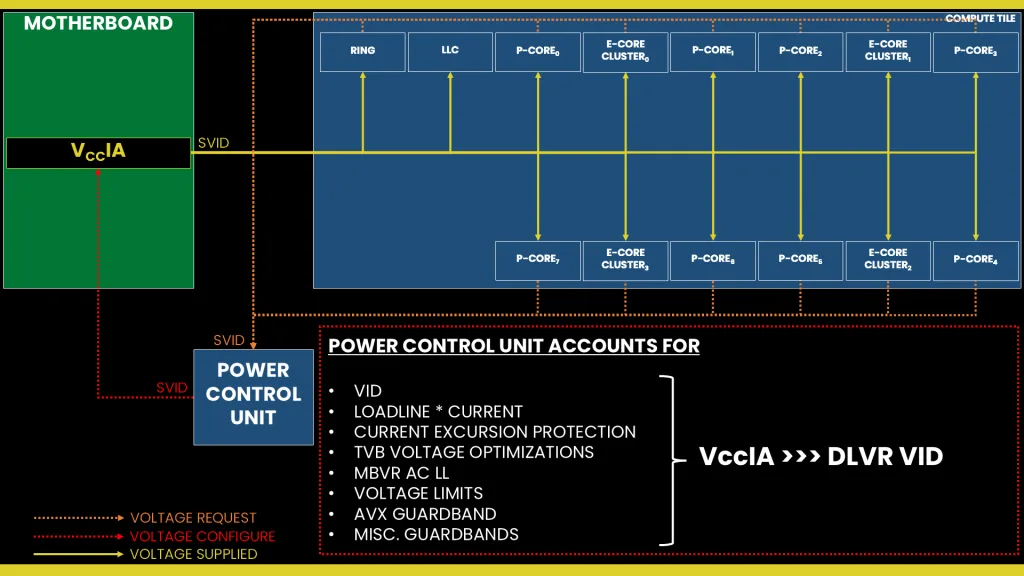

VccIA MBVR

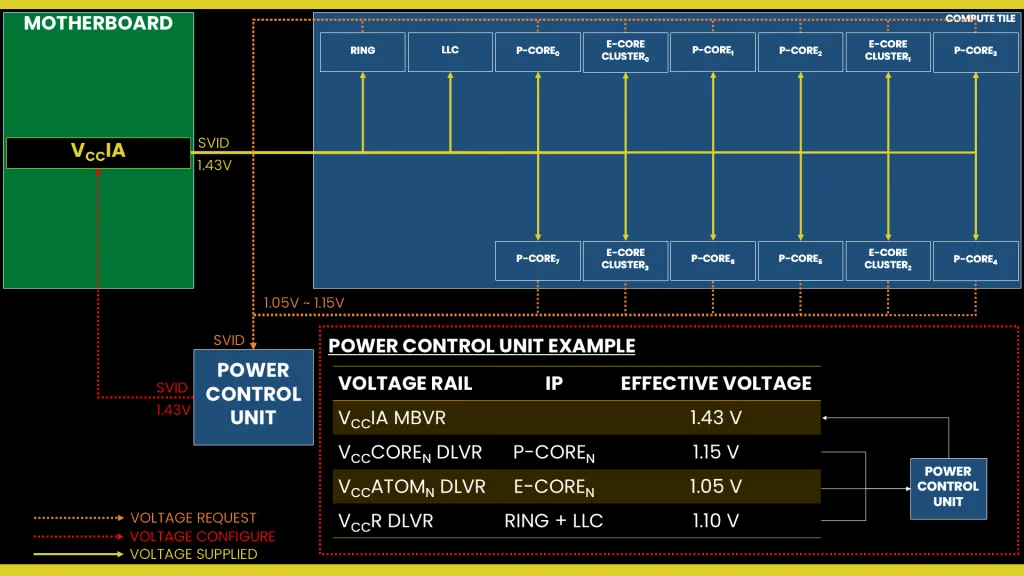

The external VccIA MBVR voltage rail provides the input voltage for the individual P-core, E-core clusters, Ring, last-level cache (LLC), and E-core L2 cache. Each P-core, E-core cluster, and Ring has an individual Digital Linear Voltage Regulator (DLVR) between the VccIA rail and the IP blocks. That means each of the blocks can operate at its own voltage.

- VccCOREn is the DLVR powering an individual P-core.

- VccR is the DLVR powering the Ring and Last-Level Cache.

- VccATOMn is the DLVR powering an individual E-core cluster, which consists of four E-cores, and its L2 cache.

The DLVRs can also be bypassed. In that case, the IP blocks are running in so-called Power Gate (PG) mode. In PG mode, the VccIA voltage rail directly powers the IP blocks, and they all share the same voltage. That’s similar to how previous generations of desktop architectures worked.

The default mode of operation is DLVR mode. Let’s explore that first.

VccATOMn DLVR Mode

Based on their VF curve, the E-core clusters request an operating voltage using the SVID protocol from the CPU Power Control Unit (PCU).

The PCU in turn configures the VccIA voltage rail and the individual VccATOMn DLVRs. There are two ways to configure the E-core voltage:

- Adaptive mode is the standard mode of operation, which relies on the factory-fused voltage-frequency curves we discussed before.

- Override mode specifies a single static voltage across all ratios. It is mainly used for extreme overclocking where stability at high frequencies is the only consideration.

We can configure override and adaptive modes directly in the PCU by specifying a target voltage and a voltage offset for each mode.

In adaptive mode, the target voltage is mapped to the E-core cluster’s “OC Ratio.” Each E-core cluster has its own “OC Ratio” which is defined by its Per Core Ratio Limit. This also matches the E-core cluster VF Point 7. You can configure the adaptive voltage and OC Ratio to any value, however, multiple rules enforce what ratio and voltage are actually set.

Rule #1: the voltage set for a given VF Point n must be higher than or equal to the voltage set for VF Point n-1.

In the case of the E-core, it means that the voltage for the OC Ratio must be higher than or equal to the voltage for VF Point 6. This can be a little strange because you can program the OC ratio to any value, including lower than 46X.

For example, let’s say you set the E-core Per Core Ratio Limit to 40X and the adaptive voltage to 1V. In that case, VF Point 7 will be programmed to 40X at 1V. However, the actual frequency will be 4.0 GHz with 1.078V, as that’s the voltage for VF Point 6.

Rule #2: for ratios between the OC Ratio and the next highest factory-fused V/f point, the voltage is interpolated between the set adaptive voltage and the factory-fused voltage.

Let’s say we configure the E-core VF OC Point to 50X and 1.25V. The target voltage for E-core ratios between 46X and 50X is now interpolated between the factory-fused voltage for 46X and the set adaptive voltage for 50X.

In the ASUS ROG BIOS, you can configure the E-core DLVR Voltage in the Ai Tweaker menu. You can configure it in adaptive, manual, and offset mode.

Two additional sidenotes about adaptive voltage.

First, the adaptive offset is applied across the entire curve. So, if we set +100 mV adaptive offset, the operating voltage for all frequencies between 8X and the OC ratio will be increased by 100 mV.

Second, any adjustments made to the V/F curve are still subject to the aforementioned rules for adaptive voltage. That includes the adjustments for the V/F Points.

For example, let’s say the E-core cluster 0 voltages for V/F Points 5 and 6 are 0.9V and 1.05V respectively. If I configure a -200 mV offset for V/F Point 6, then the effective voltage will be 0.9V, not 0.85V, because adaptive voltage Rule #1 is enforced.

Per Core Voltage

Intel Per Core Voltage allows you to set a specific target voltage for every individual E-core cluster inside your CPU. The tool is an extension of DLVR mode as it only works when DLVR is enabled. Just like in DLVR mode, you can configure the Per Core Voltage in adaptive mode and override mode, specifying a voltage for the defined Per Core Ratio Limit or across the V/F curve respectively.

The Per Core Voltage implementation for Arrow Lake is slightly different than prior platforms as each E-core cluster now has its own “OC Ratio.” Functionally, each E-core cluster’s Per Core Voltage is mapped to its Per Core Ratio Limit and, thus, also serves as the base voltage for V/F Point 7.

The standard rules for adaptive voltage mode still apply for each E-core cluster. As a consequence, it means that each E-core cluster’s V/F curve is truly independent as voltage interpolation is done for each E-core cluster separately.

Let’s say we configure the E-core cluster 1 VF OC Point to 50X and 1.25V and we set E-core cluster 2 VF OC Point to 52X and 1.30V. The target voltage for E-core cluster 1 ratios between 46X and 50X is now interpolated between the factory-fused E-core cluster 1 voltage for 46X and 1.25V for 50X. For E-core cluster 2, the ratios between 46X and 52X are interpolated between the factory-fused E-core cluster 2 voltage for 46X and 1.30V for 52X.

In the ASUS ROG BIOS, you can configure the Per E-core DLVR Voltage in the Ai Tweaker Specific Efficient Core sub-menu. You can configure it in adaptive, manual, and offset mode.

VccIA Power Gate SVID Mode

In Power Gate Mode, all the DLVRs tied to the VccIA voltage rail are bypassed and the connected IP blocks are powered directly by the VccIA voltage rail. That includes the P-cores, E-core clusters and their cache, the Ring, and the last-level cache.

Power Gate mode is basically how the VccIA rail worked on previous generation Raptor Lake processors. For Arrow Lake, it works well … but it’s a little complicated.

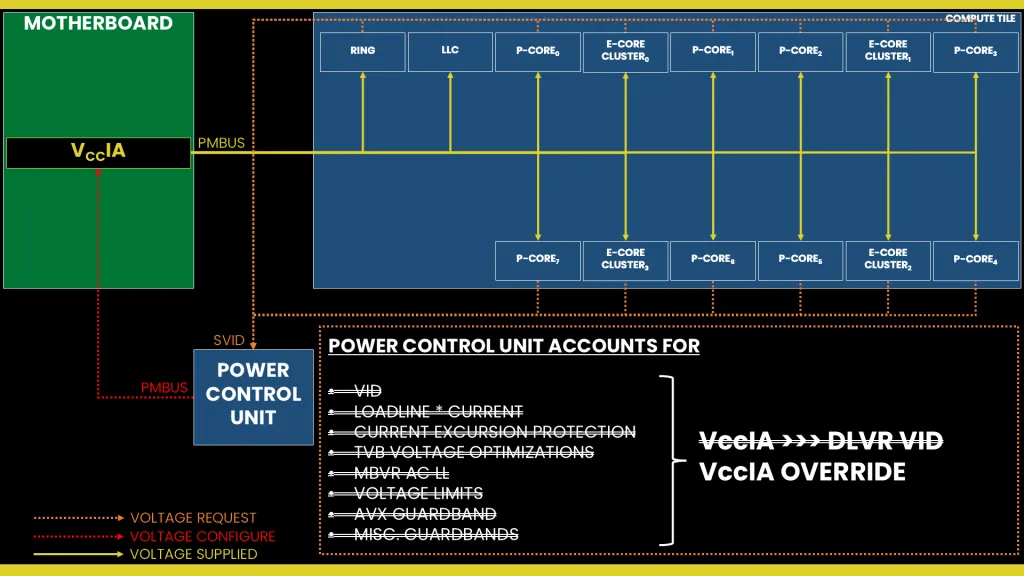

To make a long story short: when the P-cores, E-cores, and Ring requests their voltage to the CPU PCU, they account for a ton of other compensations including voltage droop, DLVR efficiency, AVX Guardband, Thermal Velocity Boost voltage optimizations, and so on. The result is that the actual voltage provided from the VccIA voltage rail to the DLVRs is relatively high!

For example, here are the voltages with the CPU at stock voltage and frequency (P53X, E46X, R39X) running a light all-core workload:

We can interpret this as follows: the P-core, E-core, and Ring request a voltage to the PCU to ensure it’s running 1.15V, 1.05V, and 1.1V respectively. The PCU then adds compensation for the loadlines, CEP, TVB, AVX, AC LL, DLVR efficiency losses, and so on. At the end of the calculation, the PCU determines the VccIA voltage rail should provide 1.43V input voltage to the DLVRs.

If we were to switch to Power Gate mode but maintain the same mechanism for calculating the required voltage, then the VccIA voltage rail would effectively provide 1.43V to the P-cores, E-cores, and Ring. That’s obviously way too high for the target frequency and would quickly result in an overheating system. But this would be how voltage was configured on previous-generation Raptor Lake processors.

VccIA Power Gate PMBus Mode

Fortunately, there’s another way to approach Power Gate Mode voltage configuration: ignore the SVID voltage requests and calculations, and program the VccIA voltage regulator directly over PMBus. This process effectively allows us to take full control over the voltage set by the VccIA voltage rail.

This approach is a very traditional way of overclocking whereby you set a fixed output voltage and then use an appropriate VRM loadline setting to reduce the operating voltage in higher load scenarios.

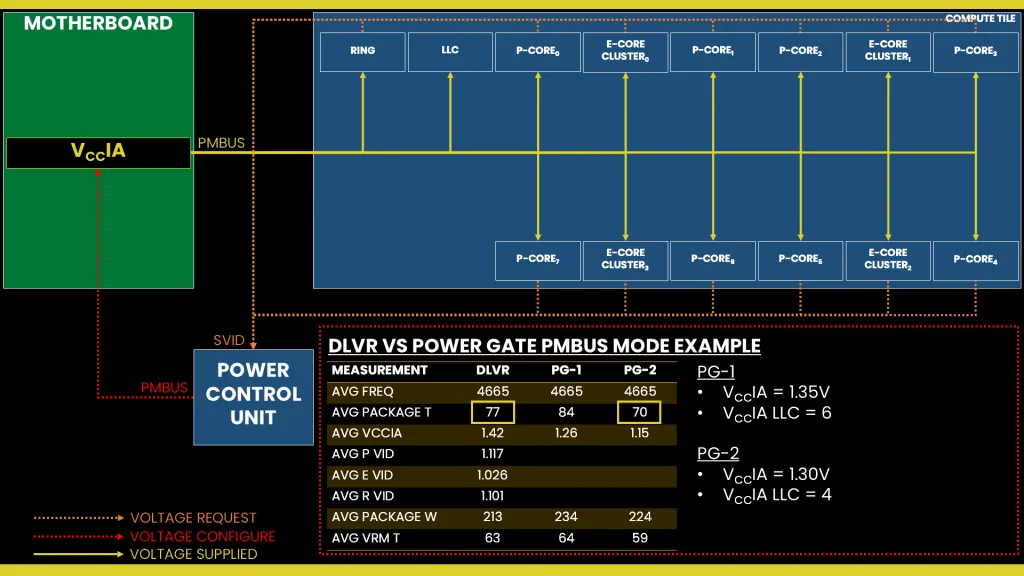

Let’s have a look at an example and compare Power Gate and DLVR in Cinebench R23.

If we set 1.35V with LLC=6, then the effective voltage under load is 1.26V. That’s about 150mV higher than with DLVR. Despite the higher voltage, the temperature is only 7C higher than when we ran DLVR.

If we set 1.30V with LLC=4, then the effective voltage under load is 1.15V which is very similar to DLVR. Despite the almost identical voltage, the temperature is 7 degrees Celsius lower than with DLVR.

The bottom line on DLVR versus PG mode is that DLVR seems to provide better temperatures and efficiency in low-load scenarios because it can have the P-core run at lower voltage. However, in high-load scenarios where the total current exceeds 150A, the power loss translates into a not-insignificant increase in temperature, which eats into the thermal budget of our thermal solution and, ultimately, lowers the overclocking headroom.

How much exactly? Well, the power loss across a linear voltage regulator equals the decrease in voltage across the DLVR multiplied by the total load.

In our example, with a voltage drop of 305mV and 160A load, the power loss is 48.8W. Nearly all of that power loss will convert into heat.

For high-load scenarios, PG mode appears to offer better overclocking headroom because the operating temperature is lower. However, we cannot rely on the PCU to control the VccIA output voltage because its calculations are too conservative. So, it ends up overvolting too much.

Therefore, the right way of overclocking using PG mode is to ignore the SVID requests entirely and take direct control of the VccIA voltage regulator. This also requires setting an appropriate VR loadline to ensure lower voltage in all-core workloads.

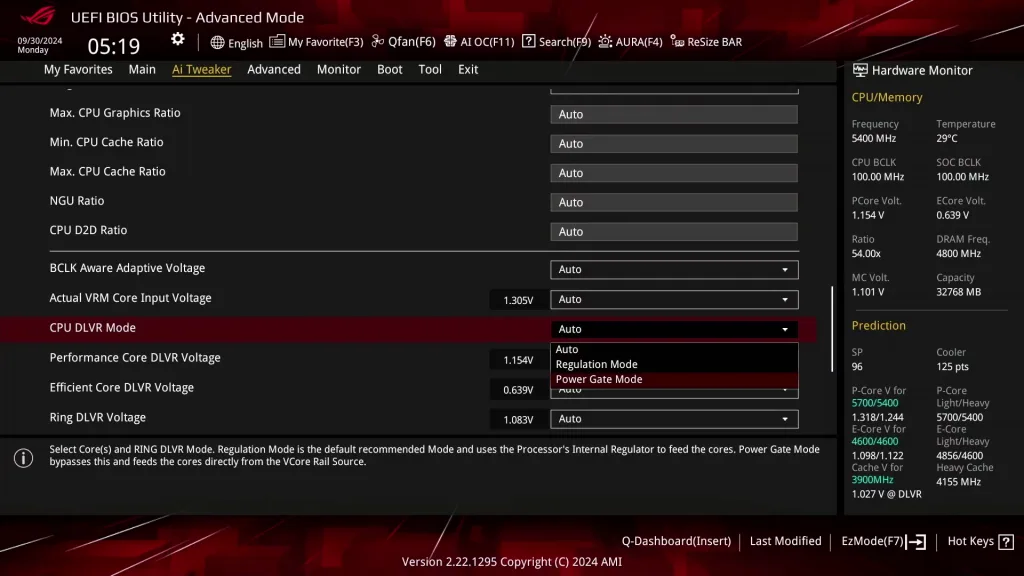

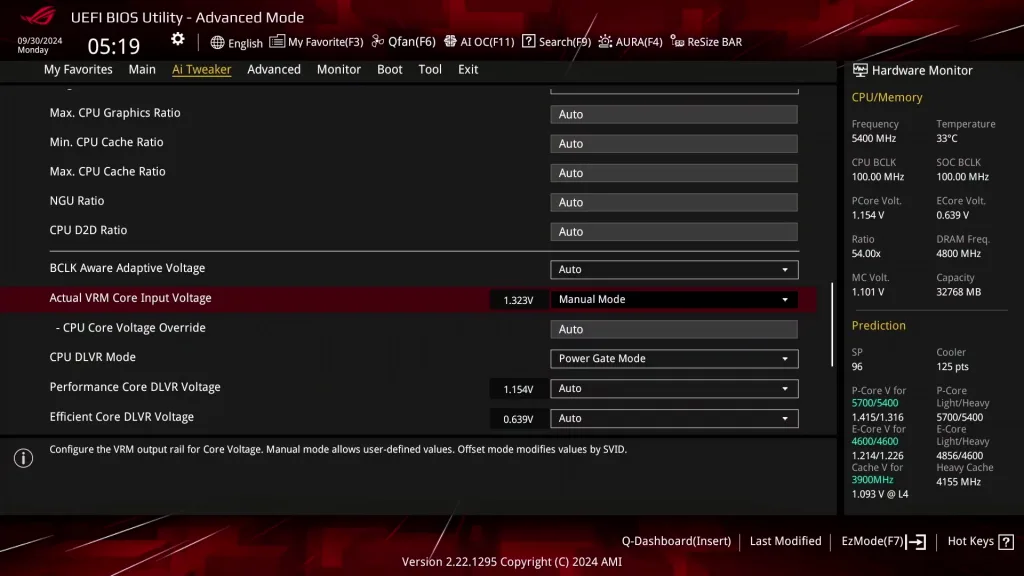

In the ASUS ROG BIOS, you can switch between DLVR and Power Gate mode for the VccIA voltage rail in the Ai Tweaker menu by configuring the CPU DLVR Mode menu item.

In the ASUS ROG BIOS, you can set the VccIA voltage rail in the Ai Tweaker menu by configuring the Actual VRM Core Input Voltage in manual mode.

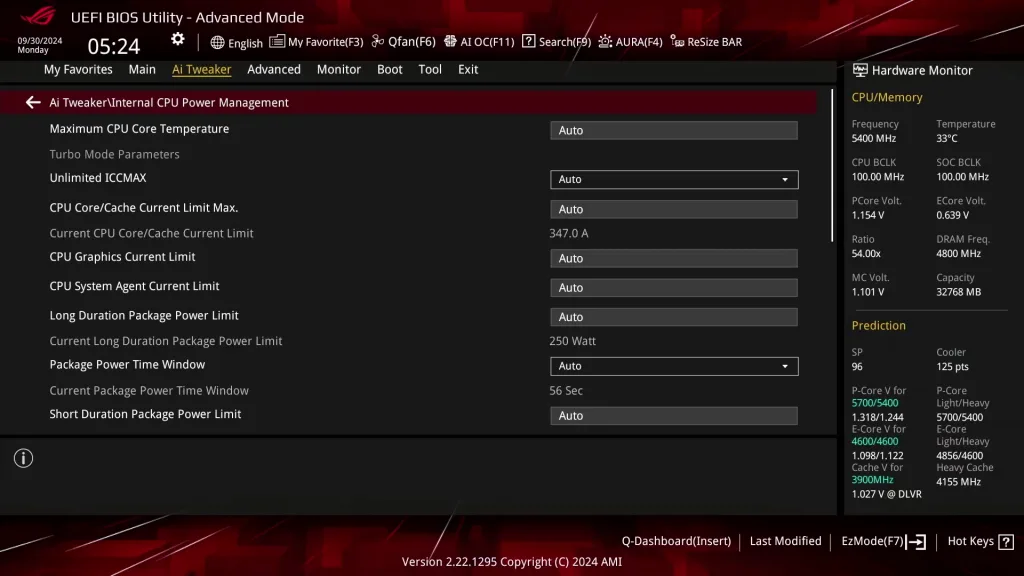

Arrow Lake E-core: Power

The processor power consumption is primarily governed by the Turbo Boost 2.0 Technology.

Turbo Boost 2.0 Technology

Intel Turbo Boost 2.0 Technology allows the processor cores to run faster than the base operating frequency if the processor is operating below rated power, temperature, and current specification limits. The ultimate advantage is opportunistic performance improvements in both multi-threaded and single-threaded workloads.

The turbo boost algorithm works according to an EWMA formula. This stands for Exponentially Weighted Moving Average. There are three main parameters to consider: PL1, PL2, and Tau.

- Power Limit 1, or PL1, is the threshold that the average power will not exceed. Historically, this has always been set equal to Intel’s advertised TDP. Very importantly, PL1 should not be set higher than the thermal solution cooling limits.

- Power Limit 2, or PL2, is the maximum power the processor is allowed to use for a limited amount of time.

- Tau is a weighing constant used in the algorithm to calculate the moving average power consumption. Tau, in seconds, is the time window for calculating the average power consumption. If the average power consumed is higher than PL1 the CPU will reduce the CPU frequency.

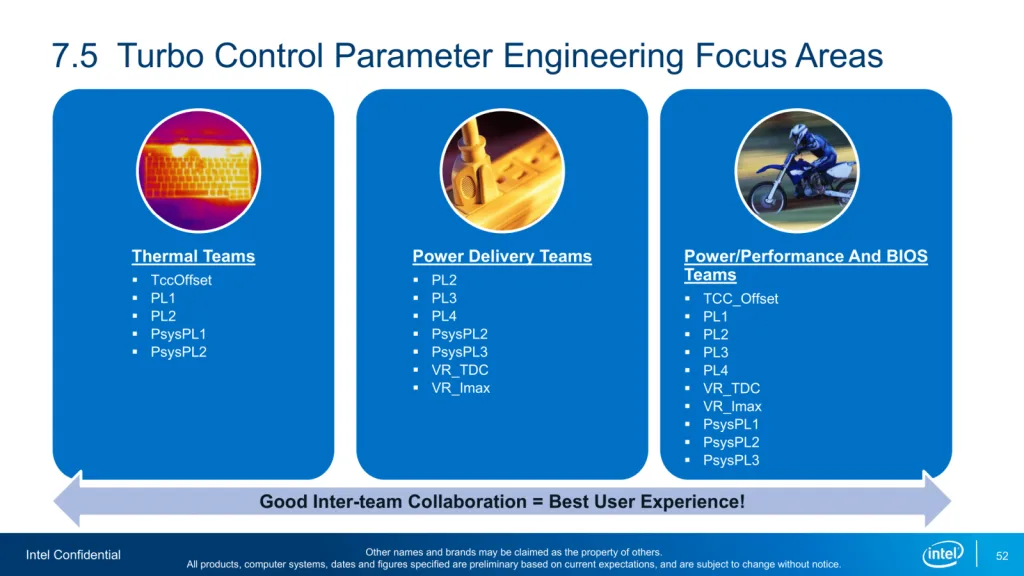

Turbo Boost 2.0 Technology has evolved over the past years to incorporate many power, thermal, and electrical performance limiters, including PL3, PL4, IccMax, TCC_Offset, VR_TDC, RATL, Pmax, and many more. To cover each in this guide would take up too much time.

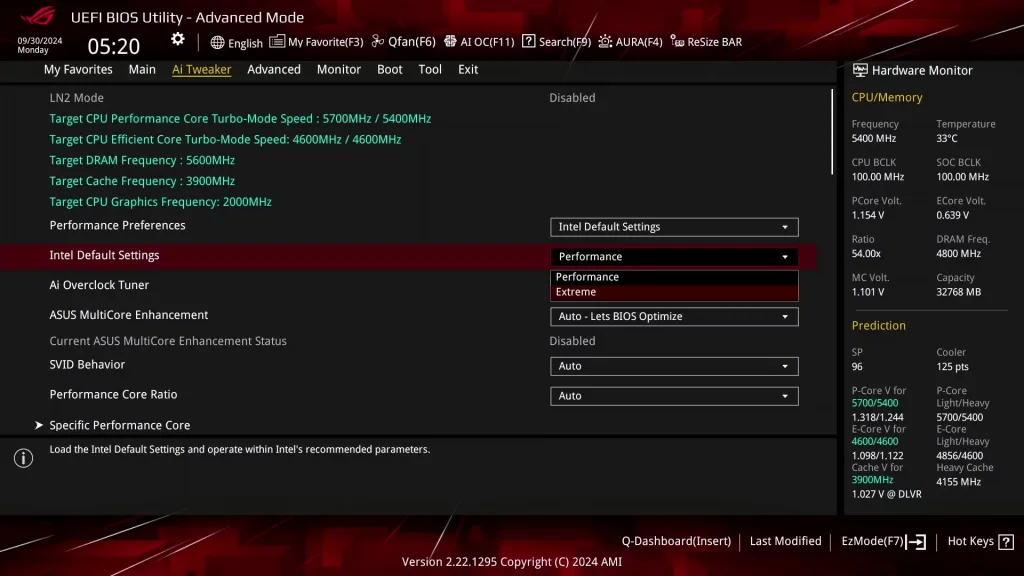

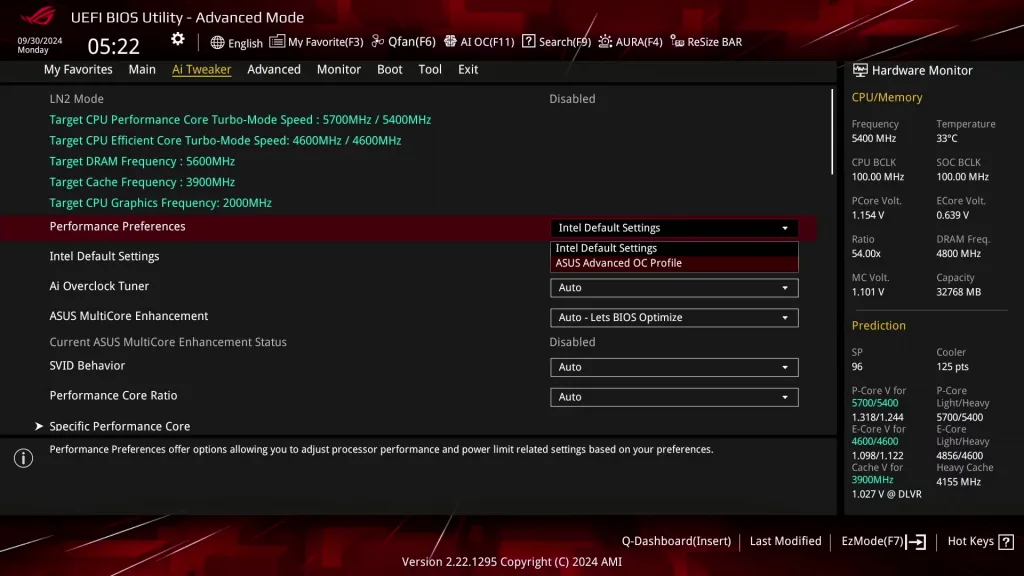

Fortunately, Intel provides two performance profiles for the Arrow Lake SKUs which configure all these settings for you. For the Core Ultra 9 285K, the Turbo Boost 2.0 profiles are Performance and Extreme.

In the ASUS ROG BIOS, you can switch between Intel Default Performance Profiles in the Ai Tweaker menu by setting the Performance Preference menu item to Intel Default Settings and selecting one of the two Intel Default Settings options.

Should you wish to override the performance profiles, you can do so in two ways: either by manually configuring them in the BIOS or by enabling ASUS Multi-Core Enhancement.

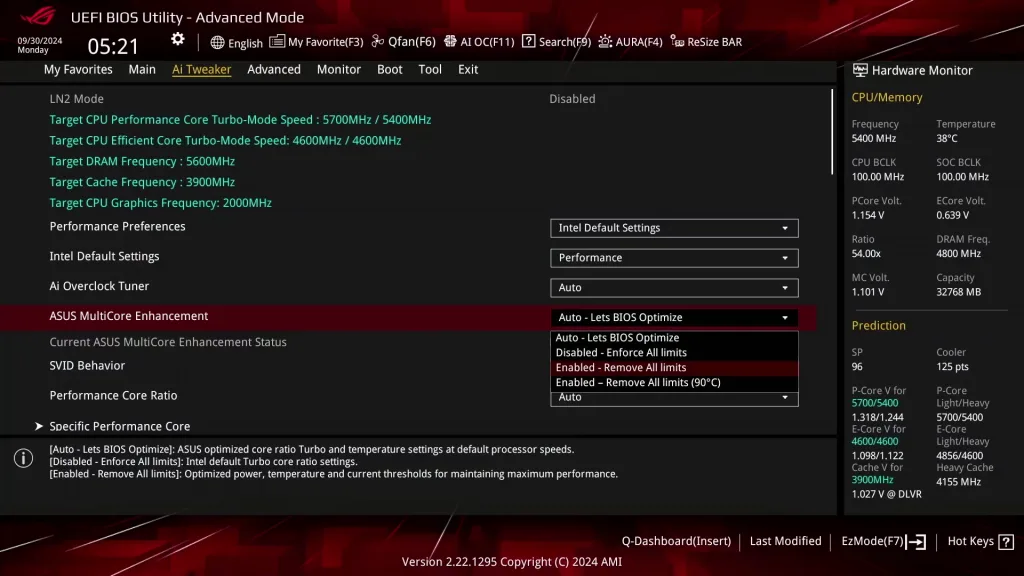

ASUS MultiCore Enhancement

ASUS MultiCore Enhancement enables higher out-of-the-box performance for heavy, power-hungry, multi-threaded workloads. It does this by optimizing the Turbo Boost 2.0 configuration. There are four available options.

- Auto, let’s the ASUS motherboard decide.

- Disabled – Enforce All Limits, following the Intel guidelines for Turbo Boost 2.0 power and ratio configuration

- Enabled – Remove All Limits, unleashes the Intel Turbo Boost 2.0 power limits for maximum performance.

- Enabled – Remove All Limits (90C), unleashes the Intel Turbo Boost 2.0 power limit but restricts the maximum CPU temperature to 90 degrees Celsius.

Note that you can select an Intel Performance Profile and enable MCE at the same time. The effect will be that MCE overrides the most common Turbo Boost 2.0 parameters such as PL1 and PL2, but will adhere to other limiters such as Current Excursion Protection (CEP) configured by the Intel Performance Preset.

In the ASUS ROG BIOS, you enable ASUS MCE in the Ai Tweaker menu.

ASUS Advanced OC Profile

The ASUS Advanced OC Profile is a more elaborate unleashed overclocking profile than MultiCore Enhancement as it not only adjusts the major Turbo Boost 2.0 parameters but also implements a lot of BIOS auto-rules to facilitate overclocking.

In the ASUS ROG BIOS, you can switch to the ASUS Advanced OC Profile in the Ai Tweaker menu by setting the Performance Preference menu item.

Arrow Lake E-core: Overclock & Undervolt

Overclocking the E-cores is similar to how it was on Raptor Lake. However, the E-cores are a lot faster and can clock higher. So, contrary to previous platforms, on Arrow Lake it’s a good idea to prioritize E-core performance tuning since it typically gives the best performance enhancement. Especially in all-core workloads.

Let’s compare the performance improvement in Cinebench R23, changing the P and E-core clock from 4.6 to 5.0 GHz. The performance improvement from overclocking the 4 E-core clusters is about twice that from overclocking the 8 P-cores.

The E-core overclocking range is also quite good. With 1.25V I could increase the E-core frequency to 5.1 GHz in Cinebench R23 with a 360 AIO. That’s a 500 MHz increase from the base frequency of 4.6 GHz.

The cores can reasonably undervolt as well. I could achieve a -75mV undervolt at 4.6 GHz, effectively reducing the operating voltage from 1.078V to 1.0V. At the lower end of the V/F curve, I could even undervolt the cores to below 0.5V at 400 MHz!